(Source: Introduction to the Power IC market 2018, Yole Développement, October 2018)

#### Large market share of LDO and DC-DC converter ICs

(Source: Yole Développement)

# 2018-2024 advanced packaging revenue forecast split by platform

(Source: Status of the Advanced Packaging Industry 2019 report, Yole Développement, 2019)

#### 50 20% CAGR2018-2024 -8% 45 16% 40 30 25 10% 20 15 Flip Chip 10 0% 2022 2023 2024 2021 Embedded Die Total -YoY growth (%) Source: Yole, 2019

# Flip Chip Capacity forecast breakdown by Flip Chip Technology

#### **Cu-pillar Market expansion**

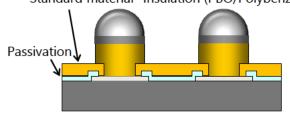

# OUME Electronics : Cu Pillar Bump Over 10 years of experience

Standard material Insulation (PBO/Polybenzoxazole)

- •Form solder height up to ½ of pillar dia.

- ·Formable up to 20um Pillar dia.

- ·RDL lamination layer (Sample result; 3 layers) ...Under development

◆ AOI Electronics : Package Assembly

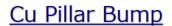

- ·Flip-chip C4.

- ·Large format matrix Lead flame

- · Wettable flank

... Under development

# Turnkey processing

①Sub 6GHz(RF) : RF-Switch/Antenna Tuning Switch etc.

⇒Low Coff, Low Insertion loss

②Power IC : DCDC Converter IC, LDO, PMIC etc.

⇒Low Inductance(Low EMI), Low Resistance

for Automotive Fsw;2MHz1, Wettable flank

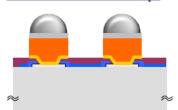

#### Cu Pillar/Micro Bump technology road map

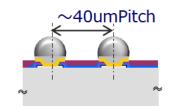

We can offer Cu Pillar Bump / Micro Bump as a terminal for flip chip connection. [Unit: μm]

| Road Map           |                       | Typical |       | 2021/M~                       |       |                       | 2022   |       |       |        |

|--------------------|-----------------------|---------|-------|-------------------------------|-------|-----------------------|--------|-------|-------|--------|

| SIZE               |                       | 6inch   | 8inch | 12inch                        | 6inch | 8inch                 | 12inch | 6inch | 8inch | 12inch |

| Þ                  | Bump Space            | NA      | 75    | 75                            | 75    | 60                    | 60     | 70    | 60    | 60     |

| Standard           | Min terminal diameter | NA      | 75    | 75                            | 75    | 60                    | 60     | 70    | 60    | 60     |

| Sta                | Max terminal height   | NA      | 65    | 65                            | 53    | 70                    | 70     | 65    | 70    | 70     |

| Custom             | Bump Space            | NA      | 50    | 70                            | NA    | 40                    | 40     | NA    | 35    | 35     |

|                    | Min terminal diameter | NA      | 50    | 70                            | NA    | 40                    | 40     | NA    | 35    | 35     |

|                    | Max terminal height   | NA      | 50    | 45                            | NA    | 65                    | 45     | NA    | 70    | 50     |

| Terminal structure |                       | SnAg/Cu |       | SnAg/Ni/Cu (8inch)<br>SnAg/Cu |       | SnAg/Ni/Cu<br>SnAg/Cu |        |       |       |        |

#### Micro Bump (Solder)

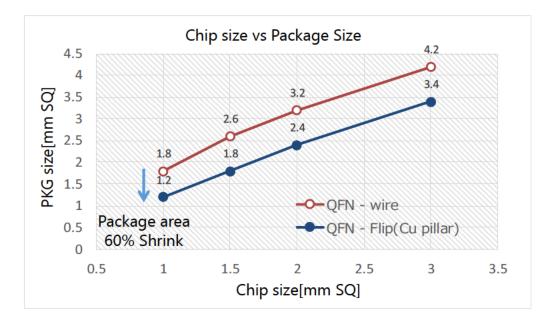

#### Advantage: Miniaturization and High functionality

| No.                   | 1             | 2        | 3         |  |

|-----------------------|---------------|----------|-----------|--|

| Package size 1.5mm SQ |               | 1.5mm SQ | 2.2mm SQ  |  |

| Chip size             | 1.33mm SQ     | 0.7mm SQ | 1.33mm SQ |  |

| PKG structure         | QFN Flip chip | QFN wire |           |  |

Package structure

Wire type

Flip chip type

Expected to be Miniaturization and highly functional (large chip size can be installed)

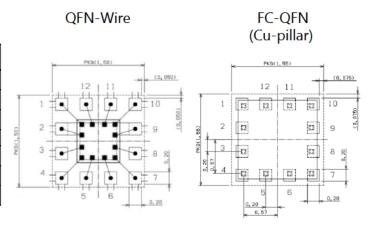

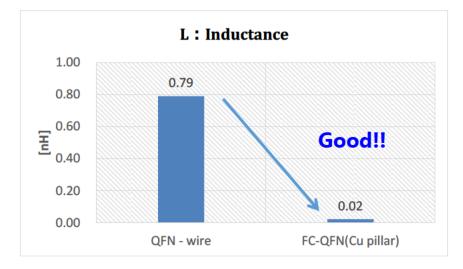

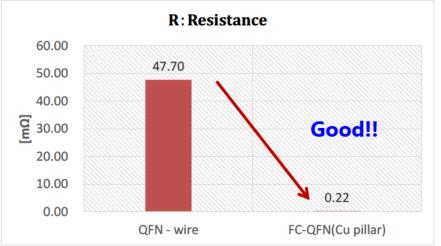

#### **Advantage: Low Electrical Parasitic properties**

Flectrical Parasitics Comparision (Per one)

| Electrical randolder companion (ref one) |              |                           |  |  |  |  |

|------------------------------------------|--------------|---------------------------|--|--|--|--|

|                                          | QFN - wire   | FC-QFN(Cu pillar)         |  |  |  |  |

| Package size [mm]                        | 1.5mmSQ      | 1.5mmSQ                   |  |  |  |  |

| Chip size [mm]                           | 0.70×0.70    | 1.33×1.33                 |  |  |  |  |

| Lead frame thickness                     | Cu 0.125mmt  | Cu 0.125mmt               |  |  |  |  |

| Internal wiring                          | Au wireΦ23μm | Cu pillarФ80µm/Height50µm |  |  |  |  |

| Terminal size                            | 0.2×0.2mm    | 0.2×0.2mm                 |  |  |  |  |

| L : Inductance [nH]                      | 0.79         | 0.02                      |  |  |  |  |

| R : Resistance [mΩ]                      | 47.70        | 0.22                      |  |  |  |  |

Flip chip QFN Packge can achieve Low Inductance and Low Resistance. Expected to improve ripple in DC-DC converter IC.

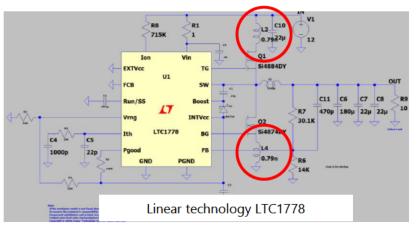

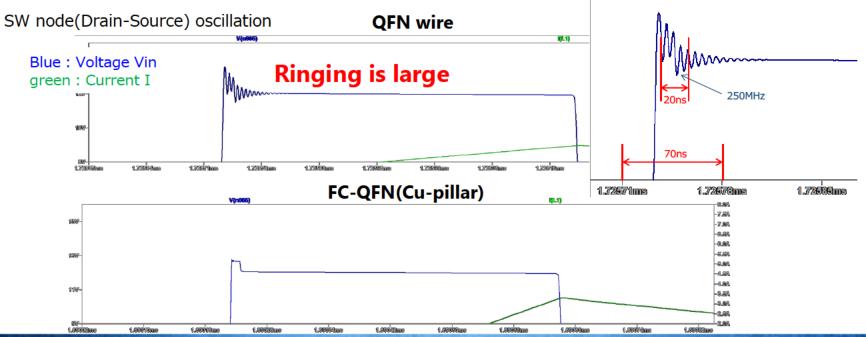

#### LTSpice @ Step down DC-DC Converter IC

#### Added parasitic Inductance

QFN wire: L=0.79nH

FC-QFN(Cu-pillar): L=0.02nH

@frequency:500kHz

#### Ringing in 250MHz class

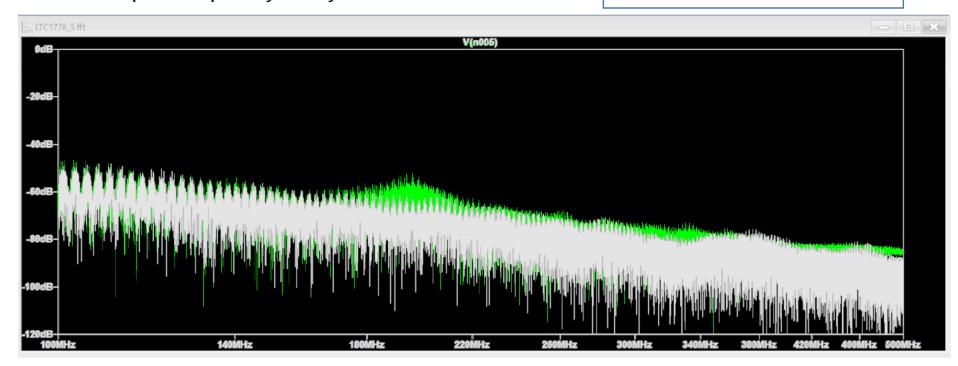

#### LTSpice @ Step down DC-DC Converter IC

FFT Output frequency analysis

QFN wire 0.79nH(green)

FC-QFN 0.02nH(gray)

EMI improvement is about 10 dB@200MHz. EMI improvement of 3 to 5 dB above 220MHz.

#### Thermal resistance Simulation(steady state)

|                   |                           | QFN wire A | QFN wire B | QFN Flip chip |  |

|-------------------|---------------------------|------------|------------|---------------|--|

| Package structure |                           |            |            |               |  |

| Package size      |                           | 1.5mm SQ   | 2.2mm SQ   | 1.5mm SQ      |  |

| Chip size         |                           | 0.7mm SQ   | 1.33mm SQ  | 1.33mm SQ     |  |

| 4-layer<br>board  | Thermal resistance [°C/W] | 153        | 103        | 88.4          |  |

| (No via)          | PD [W]                    | 0.65       | 0.97       | 1.13          |  |

• Boundary condition

※ PD: Tj=125℃, Ta=25℃

- Atmospheric temperature : 0℃ ※Assumption: No radiant heat dissipation

- Calorific value: 1W (The heat generation density is set uniformly on the chip surface.)

- Mounting board

- 1/2 symmetry (JEDEC51-7, 4-layer board 38.1x114.3xt1.6)

The heat generation density is small due to the large chip area of FCQFN

#### Thermal resistance Simulation(steady state)

|                                                       |                      | QFN wire A | QFN Flip chip |                               |                                    | QFN wire A                       | QFN Flip chip                             |

|-------------------------------------------------------|----------------------|------------|---------------|-------------------------------|------------------------------------|----------------------------------|-------------------------------------------|

| Heat<br>generation<br>density<br>[W/mm <sup>3</sup> ] |                      | 204.1      | 56.5          | ution                         | surface                            | 4                                | 56                                        |

| Heat dissipation distribution                         | Whole package        |            |               | Heat dissipation distribution | Тор                                |                                  |                                           |

|                                                       | Package expansion    |            | 8             | Heat                          | Cross-section                      | Heat diffuses in the             | Heat diffusion in the lateral             |

|                                                       | Packa                |            |               |                               |                                    | substrate thickness<br>direction | direction of the board from the terminals |

| resis                                                 | rmal<br>tance<br>/W] | 152.7      | 88.4          | []                            | 180<br>100<br>90<br>80<br>70<br>60 |                                  |                                           |

| PD [W]<br>(Tj=125°C,<br>Ta=25°C)                      |                      | 0.65       | 1.13          | ΔT [°C]                       | 50<br>40<br>30<br>20<br>10<br>0    |                                  |                                           |

#### <u>ATTENTION</u>

This material contains confidential information and it is hereby notified that any disclosure, copying, distribution, or the taking of any action in reliance on the contents of this material is strictly prohibited without a prior written consent of AOI Electronics. Thank you very much for your understanding in advance.